## 以太网收发电路

### 描述

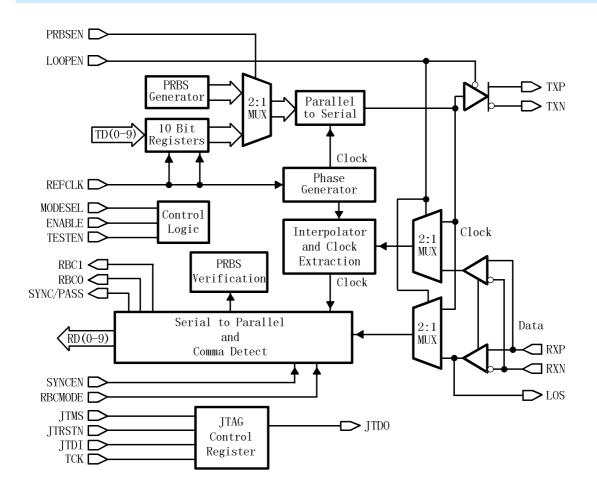

MS2201 是吉比特以太网收发器电路,可以实现超高速度的全双工数据传输。它的通信遵从 IEEE 802.3 Gigabit Ethernet 协议中的 10 比特接口的时序要求协议。MS2201 支持数据传输速率从 1Gbps 到 1.85Gbps。

## 主要特点

- 电源电压: 2.5V、3.3V

- 工作温度: -40℃-100℃

- 传输速率: 1 到 1.85 吉比特每秒 (Gbps)

- 低功耗: 在 1.25Gbps 时,小于 200mW

- 兼容 LVPECL 高速差分 I/0 接口

- 单个 PLL 锁相环

- 支持10比特接口或者5比特(双倍数据速率)接口

- 最小支持接收差模电压为 200mV 的差分信号

- 支持 3.3V 的 LVTTL 输入

- 热插拔保护

- 遵从 IEEE 802.3 Gigabit Ethernet 协议

- 遵从 IEEE 1149.1 JTAG 协议

#### 产品规格分类

| 产品     | 封 装 形 式 | 打印名称   |

|--------|---------|--------|

| MS2201 | TQFP-64 | MS2201 |

## 应用

■ 光纤通信

## 内部框图

## 极限参数

| 参数         | 符号                            | 参数范围           | 单位 |

|------------|-------------------------------|----------------|----|

| 供电电压       | VDD                           | -0.3~3.6       | V  |

| TTL 管脚输入电压 | V                             | -0.5~4         | V  |

| 其它管脚输入电压   | $V_{\scriptscriptstyle  m I}$ | -0. 3∼VDD+0. 3 | V  |

| 存储温度       | Tstg                          | $-65 \sim 150$ | °C |

| ECD        | CDM                           | 1              | kV |

| ESD        | HDM                           | 2              | kV |

## 推荐工作条件

| 参数        | 符号                                   | 测试条件                                                | 最小值 | 典型值 | 最大值  | 单位         |

|-----------|--------------------------------------|-----------------------------------------------------|-----|-----|------|------------|

| 电源电压 1    | $V_{DD}$ , $V_{DDA}$                 |                                                     | 2.3 | 2.5 | 2. 7 | V          |

| 工作电流 1    | $I_{	ext{	iny DDA}}$                 | Frequency=1.25 Gbps,<br>PRBS 形式                     |     | 80  |      | mA         |

|           |                                      | Frequency=1.6 Gbps,<br>Worst case 形式 <sup>(1)</sup> |     |     | 111  | mA         |

| 总功耗 1     | $P_{\scriptscriptstyle D}$           | Frequency=1.25 Gbps,<br>PRBS 形式                     |     | 200 |      | mW         |

| 应均和 1     | I D                                  | Frequency=1.6 Gbps,<br>Worst case形式 <sup>(1)</sup>  |     |     | 300  | mW         |

| 低功耗电流1    | $I_{	extsf{DD}}$ , $I_{	extsf{DDA}}$ | Enable=0 Vdda, Vdd=2.7V                             |     |     | 50   | uA         |

| 锁定时间 1    | PLL                                  | VDD, VDDA=2.5V,EN↑到<br>PLL锁定                        |     |     | 500  | us         |

| 工作温度 1    | T <sub>A</sub>                       |                                                     | -40 |     | 100  | $^{\circ}$ |

| 参数        | 符号                                   | 测 试 条 件                                             | 最小值 | 典型值 | 最大值  | 单位         |

| 电源电压 2    | $V_{DD}$ , $V_{DDA}$                 |                                                     | 3.0 | 3.3 | 3. 6 | V          |

| 工作电流 2    | тт                                   | Frequency=1.25 Gbps,<br>PRBS 形式                     |     | 100 |      | mA         |

| 工11中电初112 | $I_{	ext{DD}}$ , $I_{	ext{DDA}}$     | Frequency=1.6 Gbps,<br>Worst case形式 <sup>(1)</sup>  |     |     | 140  | mA         |

| 4 th #£ 0 | D                                    | Frequency=1.25 Gbps,<br>PRBS 形式                     |     | 330 |      | mW         |

| 总功耗 2     | $P_{D}$                              | Frequency=1.6 Gbps,<br>Worst case 形式 <sup>(1)</sup> |     |     | 500  | mW         |

| 低功耗电流 2   | $I_{	exttt{DD}}$ , $I_{	exttt{DDA}}$ | Enable=0 Vdda, Vdd=3.6V                             |     |     | 60   | uА         |

| 锁定时间 2    | PLL                                  | VDD, VDDA=3.3V,EN↑到<br>PLL 锁定                       |     |     | 500  | us         |

|           |                                      |                                                     |     |     |      |            |

(1) Worst case 形式指的是串行收发器转换最大密度数据的状态

## 参考时钟(REFCLK)时序要求

| 参数  | 测试条件   | 最小值       | 典型值 | 最大值       | 单位  |

|-----|--------|-----------|-----|-----------|-----|

| 频率  | 最小数据率  | 100-0.01% | 100 | 100+0.01% | MHz |

| 频率  | 最大数据率  | 185-0.01% | 185 | 185+0.01% | MHz |

| 精度  |        | -100      |     | 100       | ppm |

| 占空比 |        | 40%       | 50% | 60%       |     |

| 抖动  | 随机加确定性 |           |     | 40        | ps  |

## TTL 电学特性

| 参数      | 符号                                   | 测试条件                   | 最小值                  | 典型值   | 最大值             | 单位 |

|---------|--------------------------------------|------------------------|----------------------|-------|-----------------|----|

| 输出电压高电平 | V <sub>OH</sub>                      | $I_{oH}$ =-400uA       | V <sub>DD</sub> -0.2 |       | V <sub>DD</sub> | V  |

| 输出电压低电平 | $V_{oL}$                             | $I_{oL}=1$ mA          | GND                  | 0. 25 | 0.5             | V  |

| 输入电压高电平 | $V_{\text{IH}}$                      |                        | 1.7                  |       | 3. 6            | V  |

| 输入电压低电平 | $V_{_{\mathrm{IL}}}$                 |                        |                      |       | 0.8             | V  |

| 输入高电流   | $I_{\scriptscriptstyle \mathrm{IH}}$ | V <sub>IN</sub> =2.0V  |                      |       | 40              | uA |

| 输入低电流   | ${ m I}_{\scriptscriptstyle  m IL}$  | V <sub>IN</sub> =0. 4V | -40                  |       |                 | uA |

| 输入等效电容  | $C_{\text{in}}$                      |                        |                      |       | 4               | pF |

# 发送/接收特性

| 参 数                                          | 符号                              | 测试                        | <br>条 件                | 最小值   | 典型值  | 最大值   | 单位       |

|----------------------------------------------|---------------------------------|---------------------------|------------------------|-------|------|-------|----------|

| 发送差分信号差模电压                                   |                                 | Rt=5                      | 50 Ω                   | 600   | 850  | 1100  | ***      |

| Vod =  TxD - TxN                             |                                 | Rt=7                      | '5 Ω                   | 800   | 1050 | 1200  | mV       |

| 发送差分信号共模电压                                   | 17                              | Rt=5                      | 50 Ω                   | 1000  | 1250 | 1800  | 17       |

| (TxP + TxN)/2                                | $V_{\rm CM}$                    | Rt=7                      | '5 Ω                   | 1000  | 1250 | 1800  | mV       |

| 接收差分信号差模电压                                   |                                 |                           |                        | 000   |      | 1,000 |          |

| Vid =  RxP - RxN                             |                                 |                           |                        | 200   |      | 1600  | mV       |

| 接收差分信号共模电压                                   |                                 |                           |                        | 1000  | 1050 | 2250  | V        |

| (RxP + RxN)/2                                |                                 |                           |                        | 1000  | 1250 | 2250  | mV       |

| 接收器漏电流                                       | $I_{ikg\ (R)}$                  |                           |                        | -350  |      | 350   | uA       |

| 接收器输入电容                                      | $C_{\scriptscriptstyle \rm I}$  |                           |                        |       |      | 2     | pF       |

|                                              |                                 | 差分输出抖动                    | <b>力,随机加确</b>          |       |      |       |          |

| 串行数据总抖动                                      | t (TJ)                          | 定,PRBS 形                  | 式, R <sub>ω</sub> =125 |       |      | 0. 24 | UI       |

|                                              |                                 | MH                        | Iz                     |       |      |       |          |

| <br>  串行数据确定抖动                               | $t_{\scriptscriptstyle{(D,I)}}$ | 差分输出抖动                    | 力, PRBS 形              |       |      | 0. 12 | UI       |

| 中有效預确足行物                                     | с (рл)                          | 式, R <sub>ω</sub> =       | 125 MHz                |       |      | 0.12  | 01       |

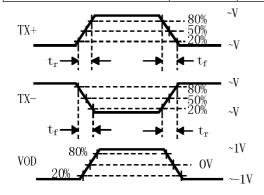

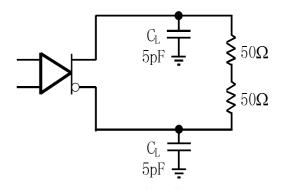

| 差分信号上升、下降时间                                  | $t_r$ , $t_f$                   | $R_L=50 \Omega$ , $C_L=0$ | 5pF,如图 1               | 100   |      | 250   | ps       |

| (20%-80%)                                    | 6 <sub>r</sub> , 6 <sub>f</sub> | 和图                        | ₹ 2                    | 100   |      | 200   | ps       |

| <br>  眼图打开的最小抖动容限                            |                                 | 差分输入抖动                    | 力,随机加确                 | 0. 25 |      |       | UI       |

| HK [2] 17 / 17 / 17 / 17 / 17 / 17 / 17 / 17 |                                 | 定, R <sub>ω</sub> =       | 125 MHz                | 0.20  |      |       | 01       |

| 接收数据在上电后的锁定                                  |                                 |                           |                        |       |      | 500   | us       |

| 时间                                           |                                 |                           |                        |       |      | 000   |          |

| 失去同步后数据重新锁定                                  |                                 |                           |                        |       |      | 1024  | Bit      |

| 时间                                           |                                 |                           |                        |       |      |       | times    |

| 发送延时                                         | $t_{d(Tx)}$                     | TBI 模式                    |                        | 19    |      | 20    | UI       |

| ///                                          | od (IX)                         | DDR 7                     |                        | 29    |      | 30    | <u> </u> |

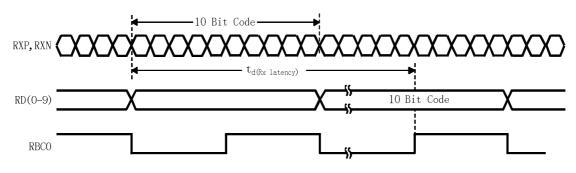

| 接收延时                                         | $t_{d(Rx)}$                     | TBI 模式                    | ,如图9                   | 21    |      | 31    | UI       |

| 1X.IV.E+1                                    | d (Rx)                          | DDR 🔻                     | 模式                     | 27    |      | 34    | O.I.     |

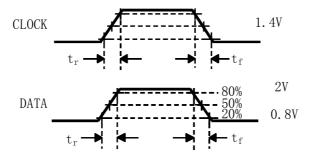

## LVTTL 输出开关特性

| 参数              | 符号                                 | 测试条件                 | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------|------------------------------------|----------------------|-----|-----|-----|----|

| 时钟上升时间          | $t_{r}(RBC)$                       | 20%-80%, C=5pF, 如图 3 | 0.3 |     | 1.5 |    |

| 时钟下降时间          | t <sub>f</sub> (RBC)               |                      | 0.3 |     | 1.5 | ns |

| 数据上升时间          | $t_{\mathrm{r}}$                   |                      | 0.3 |     | 1.5 | 20 |

| 数据下降时间          | $t_{\scriptscriptstyle\mathrm{f}}$ |                      | 0.3 |     | 1.5 | ns |

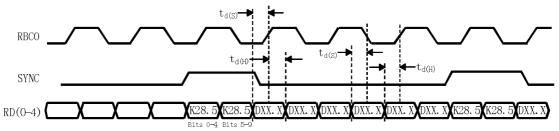

| 数据建立时间(RDO-RD9) | t <sub>su</sub> (D1)               | TDI1                 | 2.5 |     |     |    |

| 数据保持时间(RDO-RD9) | t <sub>h</sub> (D1)                | TBI normal模式,如图 6    | 2   |     |     | ns |

| 数据建立时间(RDO-RD4) | t <sub>su</sub> (D2)               | DDR 模式, R。=125 MHz,  | 2   |     |     |    |

| 数据保持时间(RDO-RD4) | t <sub>h</sub> (D2)                | 如图 7                 | 0.8 |     |     | ns |

| 数据建立时间(RDO-RD9) | t <sub>su</sub> (D3)               | TBI 半速率模式, R。=125    | 2.5 |     |     |    |

| 数据保持时间(RDO-RD9) | t <sub>h</sub> (D3)                | MHz,如图5              | 1.5 |     |     | ns |

## 发送器时序要求

| _               |                      |          |     |     |     |    |

|-----------------|----------------------|----------|-----|-----|-----|----|

| 参数              | 符号                   | 测 试 条 件  | 最小值 | 典型值 | 最大值 | 单位 |

| 数据建立时间(TDO-TD9) | t <sub>SU</sub> (D4) | TBI 模式   | 1.6 |     |     | 20 |

| 数据保持时间(TDO-TD9) | t <sub>h</sub> (D4)  | IBI 傑八   | 0.8 |     |     | ns |

| 数据建立时间(TDO-TD9) | t <sub>SU</sub> (D5) | A-th and | 0.7 |     |     |    |

| 数据保持时间(TDO-TD9) | t <sub>h</sub> (D5)  | DDR 模式   | 0.5 |     |     | ns |

| 数据上升、下降时间       | $t_r$ , $t_f$        | 如图 3     |     |     | 2   | ns |

图 1: 输出差分信号和共模电压的定义

图 2: 发送器输出端设置

图 3: AC 测量时 TTL I/O 数据的有效电平

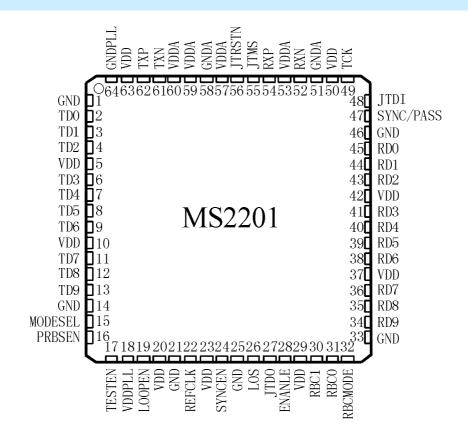

### 管脚排列图

### 管脚描述

| 管脚      |      | т /О | \#\\ <b>-</b>                          |

|---------|------|------|----------------------------------------|

| 管脚名     | 序号   | I/0  | 描述                                     |

| 信号      |      |      |                                        |

| TVD     | (2)  | DECL | 发送端的差分输出。TXP 和 TXN 作为差分串行输出接口连接        |

| TXP     | 62   | PECL | 到铜导线或光纤 I/F 单元。LOOPEN 高电平时,TXP 和 TXN 高 |

| TXN     | 61   | О    | 阻态; LOOPEN 低电平时,有效。                    |

| RXP     | 54   | PECL | 接收端的差分输入。RXP和RXN作为差分串行输入接口连接           |

| RXN     | 52   | I    | 到铜导线或光纤 I/F 单元。                        |

| REFCLK  | 22   |      | 参考时钟。REFCLK 是外置输入时钟,使接收器和发送器同步         |

|         |      |      | (100MHz-185MHz)。发送器使用该时钟存储输入数据         |

|         |      | T    | (TD0-TD9),然后送给串化器。                     |

|         |      | I    | TBI 模式下,数据在 REFCLK 的上升沿存储。             |

|         |      |      | DDR 模式下,数据在 REFCLK 的上升沿和下降沿都存储,并       |

|         |      |      | 且数据在 REFCLK 的上升沿从最高有效位开始组合。            |

| TD0-TD9 | 2-4, | т    | 发送数据。TBI 模式下(MODESEL 低电平),这些输入的 10-    |

|         | 6-9, | 1    | bit 并行数据从一个协议设备输出到收发器,再串行输出。10-        |

|           | 11-13                  |          | bit 并行数据在 REFCLK 上升沿输入到收发器,并且 TD0 作为         |

|-----------|------------------------|----------|----------------------------------------------|

|           | 11-13                  |          | 第一位串行输出。                                     |

|           |                        |          | DDR 模式下(MODESEL 高电平)仅 TD0-TD4 有效。5-bit 并     |

|           |                        |          | 行数据在 REFCLK 上升沿和下降沿输入到收发器,并且 TD0             |

|           |                        |          | 作为第一位串行输出。                                   |

| RD0-RD9   | 34,35,36,              |          | 接收数据。TBI 模式下(MODESEL 低电平),这些输出的 10-          |

| KD0-KD9   |                        |          | bit 并行数据从收发器发送到协议层。数据的输出参照 RBC0 和            |

|           | 38,39,40,<br>41,43,44, |          | RBC1 端口的时钟信号,并受所选的接收时钟模式影响。RD0               |

|           | 41,43,44,              | О        | 是第一位接收的数据。                                   |

|           | 43                     |          | DDR 模式下(MODESEL 高电平)仅 TD0-TD4 有效。RD5-        |

|           |                        |          | RD9保持低电平。5-bit 并行数据在 RBC0 上升沿输出。             |

| RBC0      | 31                     |          | 接收位时钟。RBC0 和 RBC1 是恢复时钟,使在 RD0-RD9 输出        |

| RBC1      | 30                     |          | 的 10-bit 数据同步。这两个时钟的输出受所选的接收时钟模式             |

| KDC1      | 30                     |          | 影响。                                          |

|           |                        |          | half-rate 模式下,10-bit 输出数据在 RBC0 和 RBC1 的上升沿有 |

|           |                        |          | 效。这两个时钟的相位是根据同步检测来调整到半字组边界。                  |

|           |                        |          | 在数据重组期间,时钟脉宽一直在延伸,直到数据重组结束。                  |

|           |                        | О        | RBC0 存储接收数据的位 1 和位 3, RBC1 存储接收数据的位 0        |

|           |                        |          | 和位 2。                                        |

|           |                        |          | normal-rate 模式下,仅 RBC0 是有效,且频率为 1/10 的串行数    |

|           |                        |          | 据率。数据在上升沿组合。                                 |

|           |                        |          | DDR 模式下,仅 RBC0 是有效,且频率为 1/10 的串行数据率。         |

|           |                        |          | 数据在上升沿和下降沿组合。                                |

| RBCMODE   | 32                     |          | 接收时钟模式选择。RBCMODE 和 MODESEL 都为低电平时,           |

|           |                        | т.       | RBC0 和 RBC1 端输出 half-rate 时钟。MODESEL 为低电平且   |

|           |                        | I<br>D/D | RBCMODE 为高电平时,RBC0 端输出 full-rate 时钟,RBC1 端   |

|           |                        | P/D      | 保持低电平。MODESEL 为高电平, RBCMODE 无影响,且            |

|           |                        |          | RBC0 端输出 full-rate 时钟,RBC1 端保持低电平。           |

| SYNCEN    | 24                     |          | 同步功能使能。SYNCEN 为高电平时,内置的同步功能被激                |

|           |                        | I        | 活。当这个功能被激活时,如果有要求收发器会在串行数据中                  |

|           |                        | P/U      | 检测 K28.5 逗号字符,并在位边界对数据重组。SYNCEN 为低           |

|           |                        |          | 电平时,在 RD0-RD9 上串行输入的数据是无框架的。                 |

| SYNC/PASS | 47                     |          | 同步检测标志。如果在串行数据中检测到逗号字符串,SYNC                 |

|           |                        | О        | 输出高电平。仅当 SYNCEN 有效时(高电平), SYNC 端输出           |

|           |                        |          | 同步标志脉冲。在 PRBS 测试模式下(PRBSEN 高电平),             |

|           |                        |          | SYNC/PASS 输出 PRBS 测试的结果状态(高电平表示通过)。          |

| LOS       | 26                     |          | 信号丢失标志。标志在高速差分输入端接收到的信号 RXP 和                |

|           |                        |          | RXN的丢失情况。                                    |

|           |                        | О        | 如果 RXP-RXN>150mV,LOS=1,输入信号有效                |

|           |                        |          | 如果 RXP-RXN<150mV 且>50mV,LOS 电平不确定            |

|           |                        |          | 如果 RXP-RXN<50mV,LOS=0,输入信号丢失                 |

| MODESEL | 15                                | I<br>P/D | 模式选择。选择 10-bit 接口或者 5-bit 的 DDR 接口。MODESEL 为低电平时,选择 10-bit 接口(TBI)。MODESEL 为高电平时,选择 5-bit 的 DDR 模式。当 MODESEL 空悬时,工作在                                         |

|---------|-----------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4_7 162 |                                   |          | TBI 模式。                                                                                                                                                      |

| 测试      |                                   |          | 700 比处 W 1 0 0 D D 1 之中以 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                               |

| LOOPEN  | 19                                | I        | 环路使能。当 LOOPEN 高电平时(有效),启用内置的环路。<br>发送的串行数据直接通过环路发送的接收器的输入端。在和协<br>议设备连接后,该环路就提供了自检测功能。在环路测试期<br>间,TXP 和 TXN 输出保持在高阻态。在外部串行输入和输出<br>有效的正常工作状态下,LOOPEN 必须为低电平。 |

| TCK     | 49                                | I        | 测试时钟。IEEE1149.1(JTAG)                                                                                                                                        |

| JTDI    | 48                                | I        | 测试数据输入。IEEE1149.1(JTAG)                                                                                                                                      |

| JTDO    | 27                                | О        | 测试数据输出。IEEE1149.1(JTAG)                                                                                                                                      |

| JTRSTN  | 56                                | I        | 复位信号。IEEE1149.1(JTAG)                                                                                                                                        |

|         |                                   | P/U      |                                                                                                                                                              |

| JTMS    | 55                                |          | 测试模式选择。IEEE1149.1(JTAG)                                                                                                                                      |

| ENABLE  | 28                                | I<br>P/U | 当这个端口为低电平时,使能 lddq 调试测试。RD0-RD9,RBC0,RBC1,TXP 和 TXN 处于高阻态。所以输入端的上拉和下拉电阻失效。当 ENABLE 为高电平时,设备正常工作。                                                             |

| PRBSEN  | 16                                | I<br>P/D | PRBS 使能。PRBSEN 为高电平时,PRBS 产生电路工作。在接收端的 PRBS 检测电路也开始工作。PRBS 信号输入到接收器并检测错误,在 SYNC/PASS 端显示低电平。                                                                 |

| TESTEN  | 17                                | I        | 调试测试端。                                                                                                                                                       |

|         |                                   | P/D      |                                                                                                                                                              |

| 电源      |                                   |          |                                                                                                                                                              |

| VDD     | 5,10,20,<br>23,29,37,<br>42,50,63 | 电源       | 数字电源。为所有数字电路和数字 I/O 缓冲器提供电源。                                                                                                                                 |

| VDDA    | 53,57,<br>59,60                   | 电源       | 模拟电源。为高速模拟电路,接收器和发送器提供电源。                                                                                                                                    |

| VDDPLL  | 18                                | 电源       | 锁相环电源。为锁相环电路提供电源。这个端口需要额外的滤波。                                                                                                                                |

| 地       |                                   |          |                                                                                                                                                              |

| GNDA    | 51,58                             | 地        | 模拟地。为高速模拟电路,RX 和 TX 提供接地端。                                                                                                                                   |

| GND     | 1,14,21,<br>25,33,46              | 地        | 数字地。为数字逻辑电路和数字 I/O 缓冲器提供接地端。                                                                                                                                 |

| GNDPLL  | 64                                | 地        | 锁相环地。为锁相环电路提供接地端。                                                                                                                                            |

### 功能描述

### 数据发送

MS2201 支持规定的 10 比特接口(TBI)和缩减的使用双倍时钟的 5 比特接口(DDR)。当 MODESEL 为低时,选择TBI模式;当MODESEL为高时,选择DDR模式。

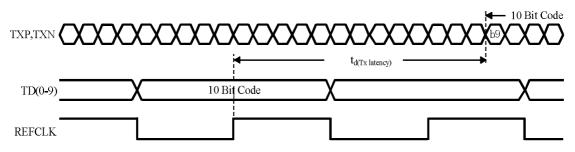

在 TBI 模式下,发送部分的寄存器在 REFCLK 信号上升沿时,存储传输进来的 10 比特位宽的 数据(8b/10b编码后的数据,TD0-TD9)。在接下来的串化器中,内部电路将 REFCLK 信号 10 倍 频后,作为移位寄存器的时钟信号。最终,在高速差分 I/0 通道上,从 bit0 到 bit9 串行地输出 8b/10b 编码后的数据。

在 DDR 模式下, 发送部分的电路通过 TD0-TD4 管脚接收位宽为 5bit 的 8b/10b 编码后的数 据。在该模式下,MS2201 同时在 REFCLK 的上升沿和下降沿采样传输进来的数据。然后,数据组 合成 10 比特位宽的数据,输送到串化器中。在 REFCLK 信号的上升沿采样 bit0-bit4,在下降沿 采样 bit5-bit9(bit0 是最先传输的数据)。

#### 传输延时

数据传输延时是指从 10 比特初始数据传输到发送部分电路后发送器最终串行输出到 bit9 数 据的延时时间。在 TBI 模式下,最小延时是 19 比特时间,最大延时是 20 比特时间。在 DDR 模式 下,最小延时是29比特时间,最大延时是30比特时间。

图 4: full-rate 模式下的发送延时

#### 数据接收

接收部分对差分信号进行解串,其中的串行数据基于相位插值器产生的时钟进行重定时。然 后, 重组成 10 比特一组的并行数据, 送到遵循接收位时钟(RBC0, RBC1)协议的协议控制器 中。

#### 接收时钟选择模式

MS2201 有两种并行总线模式: 1) 10 比特(TBI)模式: 2) 5 比特(DDR)模式。TBI模式 下,有两种可选的时钟模式通过 RBCMODE 管脚供用户选择: 1) Full-rate 时钟在 RBCO 管脚上输

出; 2) Half-rate 时钟在 RBC0 和 RBC1 管脚上输出。在 DDR 模式下,只有 full-rate 时钟在 RBC0 管脚上输出。如下表:

| <b>《 1: 侯以起拜</b> |         |               |            |  |  |  |  |  |

|------------------|---------|---------------|------------|--|--|--|--|--|

| MODESEL          | RBCMODE | MODE          | 频率         |  |  |  |  |  |

| 0                | 0       | TBI half-rate | 100-125MHz |  |  |  |  |  |

| 0                | 1       | TBI full-rate | 100-185MHz |  |  |  |  |  |

| 1                | 0       | DDR           | 100-125MHz |  |  |  |  |  |

| 1                | 1       | DDR           | 100-125MHz |  |  |  |  |  |

表 1: 模式选择

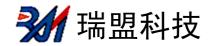

在 half-rate 模式下,两个接收时钟(RBC0 和 RBC1)相位上差 180 度,频率为二分之一的数据率。接收时钟是通过对恢复出来的时钟进行分频得到的,输出的数据以这两个接收时钟作为参照,遵从一定的协议来通过 RBC0 和 RBC1 的上升沿对输出数据进行定时。按照协议, 在 RBC1 的上升沿,接收器输出数据的 byte0 有效。如图 5:

图 5: 同步时序特性波形 (TBI half-rate 模式)

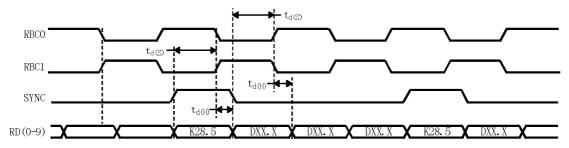

在 full-rate 模式下,只有 RBC0 时钟有效,且工作在 full-rate 模式下。接收到的数据遵从 RBC0 的上升沿输出,RBC1 为低电平。如图 6:

图 6: 同步时序特性波形 (TBI full-rate 模式)

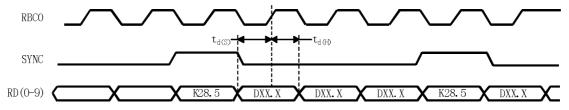

在 double data rate 模式下,接收器同时在 RBC0 的上升沿和下降沿输出数据,RBC1 为低电平。数据输出从 bit0 开始,在 RBC0 的上升沿进行重组。如图 7:

图 7: 同步时序特性波形 (DDR 模式)

MS2201 中,接收器时钟插值电路能够根据输入数据锁定相位,而不需要参考时钟。接收到的

串行数据率(RXP和RXN)和发送器发送的串行数据率一样,正常情况差±0.02%(200PPM)。

### 接收器字重组

MS2201 通过 IEEE 802.3 Gigabit Ethernet 协议定义了 10 比特的 K28.5 (逗号码) 重组方案。下面将解释这一方案怎么实现以及数据怎么重组。

### "逗号码"在预期的边界上

MS2201 集成了 10 比特 K28.5 字符串的识别与字重组功能。通过将 SYNCEN 管脚置高,可以使能 10 比特字重组功能,这样,将输入数据与 7 比特的同步码进行检验和比较的功能有效。K28.5 字符串是由 8b/10b 编码方案定义的 0011111010,其高 7 位为 0011111,也就是逗号码。K28.5 字符串就是用来组合数据的。只要 K28.5 字符串出现在预期的 10 比特边界上,接收到的 10 比特数据就能正确地组合,数据重组也就没有必要了。如图 5 所示,同步时,RBC0、RBC1、SYNC 和RD0-RD9 的时序(注意:K28.5 字符串在 RBC1 的上升沿有效)。

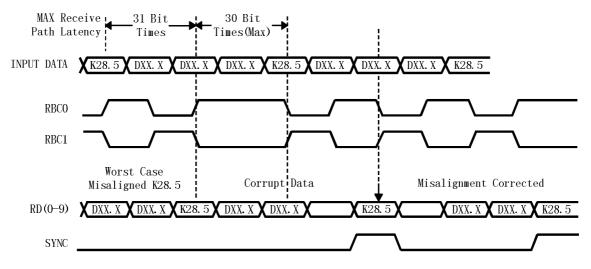

### "逗号码"不在预期的边界上

如果同步功能被使能,同时,K28.5 在预期的 10 比特字边界的两边,那么,字重组就有必要了。重组或者移位 10 比特的字边界来截去没有被组合的 K28.5 后的字符串,从而使之后的 K28.5 字符串和随后的所有数据正确组合,如图 8 所示。在重组过程中,RBC0 和 RBC1 的脉冲宽度会在当前的状态上延伸或者保持。基于这个设计,最大的延伸宽度是 20 比特时间。当 K28.5 在 RBC1 的下降沿组合数据,而不是在 RBC1 的上升沿时(worst case scenario),上述这种情况才会出现。如图 8 所示,数据重组时的时序特性。

图 8: 字重组时序特性波形

如果系统不需要数据包,那么可以置低 SYNCEN 管脚关闭数据组合功能。

当同步字符串被发现后,SYNC 信号会被置高,同时数据会根据 K28.5 字符串进行组合。在 TBI 模式下,SYNC 脉冲的持续时间与数据宽度一样。在 DDR 模式下,SYNC 的脉冲持续时间与 RBCO 的周期相等。

#### 数据接收延时

串行数据到并行数据的延时指的是从接收器接收到第一个比特数据到输出组合后的并行数据的时间,其中,RD0 是第一个被接收的数据。在 TBI 模式下,最小的延时是 21 比特时间,最大的延时是 31 比特时间。在 DDR 模式下,最小的延时是 27 比特时间,最大的延时是 34 比特时间。

图 9: 接收延时 (TBI normal 模式)

## 信号丢失检测

MS2201 有一个信号丢失检测电路,该电路用于限制那些没有足够的电压来使时钟恢复电路保持稳定的输入信号。LOS 管脚用于指示较差的输入信号,比如较远的电缆或者没有信号被传输,不会对符合要求的信号指示。在 PRBS 作为串行输入的情况下,信号幅度大于 150mV 时,LOS 信号是高电平,信号幅度小于 50mV 时,LOS 信号是低电平,信号幅度在 50mV 和 150mV 之间时,LOS 信号不确定。

#### 可测试性

MS2201 中 LOOPBACK 功能提供了发送/接收部分电路的全速度测试。同时,ENABLE 功能能够关闭所有的内部电路,这样就可以进行 lddq 测试了。PRBS 功能同样提供了 BIST(built-in self test)测试。将 TESTEN 置高,使能 lddq 测试模式。在 TESTEN 端口上有一个内部的下拉电阻,所以,默认状态下 MS2201 是正常工作。TESTEN 测试只是用于生产调试,不面向终端用户。

#### LOOPBACK 测试

MS2201 收发器通过使能内部环路(L00PEN 置高)来启用自测试功能。一旦启用这一功能,串行的传输数据将直接通过内部电路接到接收器上。通过比较输出的并行数据和输入的并行数据来进行功能验证(在 L00PBACK 测试时,外部差分输出端口 呈高阻态)。

#### ENABLE 功能

ENABLE 为低时,所有的模拟电路和数字电路的静态电源将被关闭。有利于在链接上没有数据传输时,使 MS2201 处于低功耗空闲状态。

#### PRBS 功能

MS2201 有内置的 2<sup>7</sup>-1 PRBS(伪随机序列)测试功能。当 PRBSEN 控制位被置高时,启用 PRBS 测试功能。在发送端,伪随机序列产生并送到 10 比特的发送器输入总线上。在 PRBS 测试模式下,正常情况下的并行输入端口上的数据将被忽略。然后,伪随机序列就像正常的数据一样经过发送器电路,最后由发送器输出。该输出可以被送到 BERT(bit error rate tester)测试仪或者是送到另外一颗 MS2201 的接收端。既然伪随机序列不是真正的具有随机性,而是一串预先规定的由"0"、"1"组成的序列,那么数据可以被 BERT 捕获和检查是否出错。在 MS2201 的接收端,当然也有一个受控于 PRBSEN 信号的内置 BERT 功能。它能够接收伪随机数据,并检查是否出错,通过拉低 SYNC/PASS 管脚上的信号来标志有错误。启用 PRBS 功能时,RBCMODE 控制信号高电平或者低电平没有影响。但是,MODESEL 必须为低电平才能使伪随机序列检验功能工作正常。同时,MS2201 工作在 TBI 模式,RBC0 管脚上输出一个 full-rate 时钟。PRBS 测试功能支持两种模式(normal 和 latched),由 SYNCEN 控制。当 SYNCEN 为低时,伪随机序列的误码率测试结果将通过 SYNC/PASS 端口输出。当 SYNCEN 为高时,伪随机序列的检验结果将被锁存在 SYNC/PASS 端口上(检测到一次错误,SYNC/PASS 端口就被锁在低电平)。

#### **JTAG**

MS2201 支持遵从 IEEE 1149.1 协议的 JTAG 功能。如果需要使用 JTAG 功能,那么 5 个 JTAG 脚: TRSTN、TMS、TCK、TDI、TDO 可以当做通常定义下的 JTAG 管脚使用。如果不需要使用 JTAG 功能,推荐将 TRSTN 接到地上,TMS 和 TDI 由于内部有上拉电阻,所以可以不接,TDO 是输出脚,可以不接,TCK 内部没有上拉电阻,可以接到 GND 上。如果 TRSTN 已经接低,TCK 如果不用可以不接任何信号。

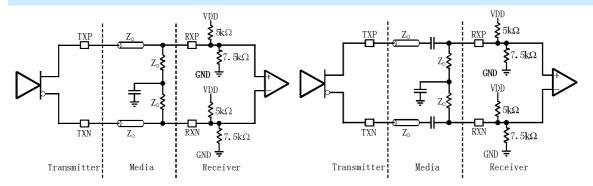

## 典型应用电路图

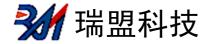

图10: 高速I/O直流耦合

图11: 高速I/O交流耦合

图12: 典型应用电路(交流耦合)

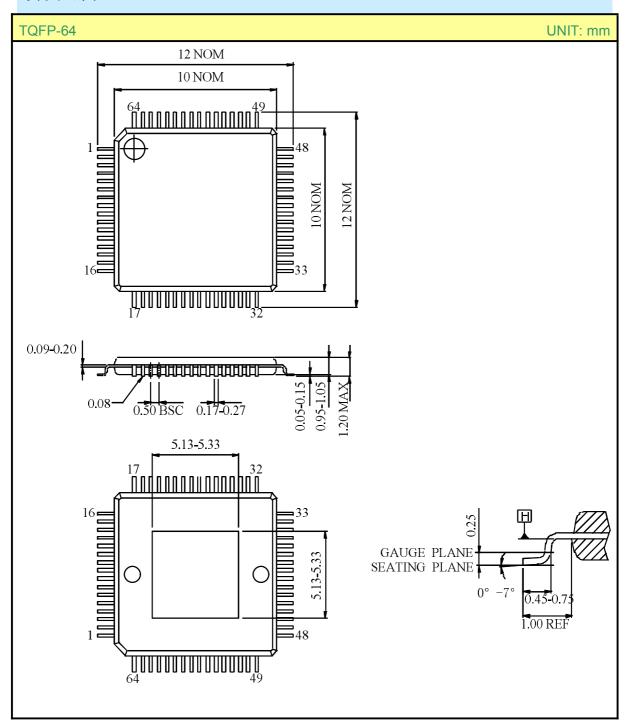

## 封装外形图

### MOS电路操作注意事项:

静电在很多地方都会产生,采取下面的预防措施,可以有效防止MOS电路由于受静电放电影响而引起的损坏:

- 操作人员要通过防静电腕带接地。

- 设备外壳必须接地。

- 装配过程中使用的工具必须接地。

- 必须采用导体包装或抗静电材料包装或运输。